| 6.      | (a)                                                                  | What are various design constraints of                              | a                 | No. of Printed Pages: 04                              | Roll No                     |

|---------|----------------------------------------------------------------------|---------------------------------------------------------------------|-------------------|-------------------------------------------------------|-----------------------------|

|         |                                                                      | CMOS compartor ?                                                    | 5                 |                                                       |                             |

|         | (b)                                                                  | What are various methods o                                          | of                | <b>BB-64</b>                                          |                             |

|         |                                                                      | compensating 2 stage Op-Amp. 10                                     |                   | M. Tech. EXAMINATION, Dec. 2017                       |                             |

| Unit IV |                                                                      |                                                                     | (Second Semester) |                                                       |                             |

| 7.      | (a)                                                                  | Implement a simple PLL in CMOS                                      |                   | (B. Scheme) (Re-appear Only)                          |                             |

|         |                                                                      | technology.                                                         | 5                 | ECE/Industry Integrated MTEC-508-B                    |                             |

|         | (b)                                                                  | Write short notes on the following:                                 |                   |                                                       |                             |

|         |                                                                      | <ul><li>(i) PLL as frequency multiplier</li><li>(ii) OTA.</li></ul> |                   | ANALOG VLSI DESIGN                                    |                             |

| 8.      | What are various types of CMOS ADC?  Model a generalized ADC in CMOS |                                                                     | Time: 3 Hours]    | [Maximum Marks: 75                                    |                             |

|         |                                                                      |                                                                     | S                 | Before answering the question-paper candidates        |                             |

|         | tech                                                                 | nnology.                                                            | 15                | should ensure that they have been supplied to correct |                             |

|         |                                                                      |                                                                     |                   | and complete question-paper. No complaint, in this    |                             |

|         |                                                                      |                                                                     |                   | regard, will be entertained after the examination.    |                             |

|         |                                                                      |                                                                     |                   | Note: Attempt Five ques                               | stions in all, selecting at |

M-BB-64 4 60 (3-44/13)M-BB-64 P.T.O.

least one question from each Unit. All

questions carry equal marks.

## Unit I

- 1. (a) Explain graphically, the variation of Gate-Source and Gate-Drain capacitance with Gate-Source Voltage.

- (b) Discuss SPICE level-3 Model for CMOS.

8

- **2.** (a) Model MOSFET as Diode. **9**

- (b) Draw MOS schematic of cascode current sink. 6

## **Unit II**

- 3. (a) Derive transconductance of source follower.

- (b) What are advantages of differential amplifier? Draw its small signal equivalent.

2

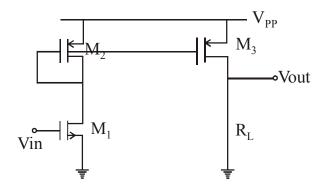

4. (a) Calculate small signal voltage gain of the following circuit: 5

(b) What are application areas of Wilson current mirror? Draw and explain its small signal equivalent.10

## **Unit III**

- 5. (a) Design a cascode Op-Amp for maximum differential swing of 2.4 V, total power dissipation of 6 mW.

- (b) Explain concept of Gain Boosting in Op-Amp.5

3

(3-44/14)M-BB-64

P.T.O.